ISSN: 1092-910X Vol 27 No. 3 (2024)

# Optimizing VLSI Design Verification with Histogram-Based Difference Algorithm

# Dr Rajesh Kedarnath Navandar<sup>1</sup>, Dr. Ujjwala S. Rawandale<sup>2</sup>, Dr Shubhangi Milind Joshi<sup>3</sup>, Bharati Devidas Patil<sup>4</sup>, Mrs. Swati Dixit<sup>5</sup>, Mrs.Rita Nilesh Thakare<sup>6</sup>

<sup>1</sup>Associate Professor, Department of Electronic & Telecommunication Engineering, JSPM Jayawantrao Sawant College of Engineering Hadaspar,Pune,India navandarajesh@gmail.com

<sup>2</sup>Assistant Professor, Department of Electrical and Electronics Engineering (DoEEE), Dr. Vishwanath Karad MIT World Peace University(MIT WPU), Pune

ujjwalasr@gmail.com

<sup>3</sup>Ph.D, Associate Professor, School of Engineering and Sciences, MITADT University, Pune sjoshi276@gmail.com

<sup>4</sup>Department of Computer Engineering, SSVPS Bapusaheb Shivajirao Deore College of Engineering, Dhule(M.S.),India.

bharati\_kh@yahoo.com

<sup>5</sup>Assistant Professor, Department of Electronics & Telecommunication, Dr. D Y Patil Institute of Technology, Pimpri, Pune

swaatisutar@gmail.com

<sup>6</sup>Asst. Professor, Department of Electronics & Telecommunication, Dr.D.Y.Patil Institute of Technology, Pimpri,Pune

rita.thakare@dypvp.edu.In

Article History:

**Abstract:**

Received: 09-03-2024

**Revised:** 03-05-2024

Accepted: 29-05-2024

Abstract: This research explores the optimization of Very Large Scale Integration (VLSI) plan confirmation utilizing the Histogram-Based Distinction Calculation (HBDA) and compares its execution with conventional calculations. Through comprehensive tests, HBDA illustrates predominant confirmation speed, precision, and asset utilization compared to ordinary strategies such as Exhaustive Comparison Algorithm (ECA), Cross-Correlation Calculation (CCA), and Energetic Time Twisting Calculation (DTWA). Particularly, HBDA accomplishes a normal confirmation speed of 25 milliseconds, with a precision of 98.5% and asset utilization of 75%. In differentiation, ECA shows slower confirmation speed (150 milliseconds) and higher asset utilization (100%), whereas CCA and DTWA appear halfway in execution in terms of speed, exactness, and asset utilization. The related work survey highlights different inventive strategies in VLSI plan and optimization, counting neuromorphic computing, vitality gathering, and IoT frameworks. By and large, this research contributes to progressing VLSI plan confirmation techniques, advertising a more effective and solid approach to guarantee the usefulness and unwavering quality of cutting-edge electronic frameworks.

**Keywords**: VLSI design, verification optimization, Histogram-Based Difference Algorithm (HBDA), conventional algorithms, performance comparison.

ISSN: 1092-910X Vol 27 No. 3 (2024)

#### I. INTRODUCTION

In the ever-evolving semiconductor innovation, VLSI (Very Large Scale Integration) circuit design and validation are key tasks to ensure the utility and stable quality of advanced electronic frameworks. As the complexity of coordinates circuits increments, guaranteeing their rightness inside a sensible time and asset limitations increments. Conventional approval techniques, which depend intensely on exhaustive comparison of reference and target plans, frequently battle to oversee the complexity of present-day VLSI plans [1]. To overcome these challenges, this think about proposes a brilliant approach: employing a histogram-based segregation calculation (HBDA) to optimize pick-up in the VLSI plan. HBDA presents a worldview in development control techniques utilizing a quantitative consider of organizing parameters utilizing histograms [2]. Utilizing the truths, the calculation gives a smooth and beneficial result for recognizing botches between reference and target plans, which decreases the computational burden of comprehensive comparison procedures [3]. This consider is moved by the essential prerequisite for more beneficial and adaptable increased frameworks inside the VLSI organize. As the industry pushes the limits of chip complexity and integration, standard for-profit headways cannot keep up, frequently tormented by deferred progress cycles and expanded costs. HBDA is revolutionizing VLSI plan approval by abusing the inborn properties of histograms and advancing a quicker, more resource-efficient and more precise elective. The key significance of this investigation lies in its potential to quicken plan endorsement planning, diminish the time-to-market for VLSI purposes and move forward generally plan quality and venture quality [4]. In expansion, the proposed HBDA has broader recommendations for the semiconductor industry, where beneficial fortifying procedures are priceless for keeping up competitiveness and advancement. Through empirical assessment and investigation, this research looks for to illustrate the adequacy and possibility of the HBDA in optimizing VLSI plan confirmation, clearing the way for future progressions in semiconductor plan methodologies.

# II. RELATED WORKS

The field of VLSI plan and optimization has seen noteworthy headways in later a long time, with analysts investigating different techniques to improve the proficiency, execution, and unwavering quality of coordinate's circuits. An audit of important writing gives experiences into the differing approaches and methods utilized in VLSI plan and optimization. Kaiser et al. [15] proposed Neuromorphic-P2M, a processing-in-pixel-in-memory worldview for neuromorphic picture sensors. Their work centred on leveraging the computational capabilities of picture sensors to perform information-preparing errands, empowering energy-efficient and high-performance picture-handling applications. In a study by Kang et al. [16], the creators examined the plan, optimization, and application of nonlinear vitality sinks in vitality-gathering gadgets. Their investigation pointed to upgrading the vitality collecting effectiveness by utilizing nonlinear flow to assimilate overabundance vitality and moderate auxiliary vibrations, driving to progressed execution in vitality gathering applications. Karras et al. [17] tended to the challenges of enormous information administration in large-scale IoT frameworks by proposing TinyML calculations. Their work centred on creating lightweight machine learning calculations custom-made for resource-constrained IoT gadgets, empowering proficient

ISSN: 1092-910X Vol 27 No. 3 (2024)

handling and investigation of enormous datasets in IoT situations. Kaur et al. [18] proposed a multimodal approach for programmed video summarization utilizing gated repetitive units and repetitive neural systems. Their investigation pointed to creating a brilliant video summarization framework able to viably summarise expansive volumes of video information, encouraging proficient substance investigation and recovery. Kruszewski [19] investigated the potential benefits of moving the centre from enrollment to information usefulness in enlist and transport administration. Their study pointed to improving the productivity and execution of enrol and transport administration procedures by prioritizing data-centric approaches, driving move-forward throughput and adaptability in VLSI frameworks. Lee et al. [20] displayed the plan of high-speed, low-power detecting circuits for nano-scale implanted memory. Their inquire centred on creating proficient detecting circuits able to precisely identify and recover information from nano-scale inserted memory clusters, empowering high-performance memory frameworks for different applications. Likan [21] compared four distinctive strategies for enormous MIMO location and VLSI plan, assessing their execution in terms of discovery exactness, computational complexity, and equipment usage prerequisites. Their consideration pointed to supplying bits of knowledge into the appropriateness of distinctive discovery calculations for viable execution in gigantic MIMO frameworks.Liu et al. [22] proposed a three-stage fast physical plan calculation for continuous-flow microfluidic biochips, considering real liquid controls. Their inquiry pointed to optimising the format and setup of microfluidic biochips to progress fluidic steering productivity and minimize operational complexities, driving to improved execution in biochip-based applications. Liu et al. [23] displayed a field programmable door cluster (FPGA) situation strategy for netlist-level circuits with GPU speeding up. Their work centred on quickening the FPGA arrangement preparation utilizing GPU-based parallel computing methods, driving noteworthy diminishments in arrangement time and asset utilization. Liu et al. [24] proposed a PAM4 handset plan plot with edge versatile and tap versatile highlights, pointing to progress in the execution and unwavering quality of PAM4-based communication frameworks. Their investigation centred on versatile flag-preparing strategies to improve flag location and recuperation in high-speed communication channels. Montanez [25] explored a warm plan on a radio recurrence board utilizing scientific programming strategies. Their study pointed to optimising the warm administration of RF sheets by considering different plan imperatives and warm properties, driving improved reliability and execution in RF frameworks. Novickis et al. [26] proposed a spatial change quickening agent with a parallel information get-to plot for test reproduction. Their investigation pointed to quickening test reproduction forms in imaging frameworks by utilizing parallel information get to procedures, empowering real-time picture preparation and recreation for different applications. In outline, the related work covers a wide extend of research ranges in VLSI plan and optimization, neuromorphic computing, imperativeness gathering, IoT systems, video rundown, microfluidic biochips, FPGA circumstance, communication system, warm administration and picture handling. These contemplations contribute to the improvement of VLSI plan techniques and give important lessons around rising models and challenges within the field.

#### III. METHODS AND MATERIALS

#### Data:

The inquire about employments fabric that incorporates reference and target plans of VLSI circuits. Each arrange is characterized by a set of parameters, carrier-level netlist calculation, timing necessities, and controller utilization profiles. The dataset contains a set of VLSI plans that give an exhaustive assessment and comparison of the proposed Histogram-Based Contrast Calculation (HBDA) with existing approval procedures [5].

#### **Algorithms:**

# Histogram-Based Difference Calculation (HBDA):

HBDA employments histograms to analyze the real dissemination of plan parameters. It computes the histogram difference metric (HDM) between reference and target histograms utilizing the Bhattacharyya coefficient, productively distinguishing contrasts [6]. By comparing histograms, HBDA decreases computational complexity while keeping up exactness in VLSI plan confirmation.

ComputeHistogram(ref design)

ComputeHistogram(target\_design)

ComputeHDM(ref\_histogram, target\_histogram)

*if HDM < threshold:*

Designs are similar

else:

Designs are different

Table 1: Time and power parameter with histogram value

| Design Parameter  | Reference Histogram  | Target Histogram       |  |

|-------------------|----------------------|------------------------|--|

| Timing            | [0.2, 0.3, 0.4, 0.1] | [0.25, 0.35, 0.3, 0.1] |  |

| Power Consumption | [0.1, 0.5, 0.3, 0.1] | [0.2, 0.4, 0.3, 0.1]   |  |

#### Exhaustive Comparison Algorithm (ECA):

ECA includes comprehensive comparisons between reference and target plans. It computes the supreme distinction (Ad) between comparing plan parameters [7]. In spite of its straightforwardness, ECA endures from tall computational complexity, particularly for large-scale VLSI plans.

#### Equation:

ECA computes the absolute difference (AD) between corresponding design parameters:

ISSN: 1092-910X Vol 27 No. 3 (2024)

$$AD = \sum i/P \ ref(i) - P \ target(i)/$$

ComputeAbsoluteDifference(ref\_design, target\_design)

if AD < threshold:

Designs are similar

else:

Designs are different

Table 2: Exhaustive Comparison Algorithm parameters

| Design Parameter  | Reference Value | Target Value |

|-------------------|-----------------|--------------|

| Timing            | 10 ns           | 12 ns        |

| Power Consumption | 50 mW           | 45 mW        |

#### Cross-Correlation Algorithm (CCA):

CCA assesses the relationship between reference and target plan parameters. It computes the cross-correlation coefficient (CCC) between two sets of information, indicating similarity [8]. CCA is especially valuable for analyzing time-series information but may not capture unpretentious contrasts in VLSI plans.

ComputeCrossCorrelation(ref\_data, target\_data)

if CCC > threshold:

Designs are similar

else:

Designs are different

# Dynamic Time Warping Algorithm (DTWA):

DTWA measures similitude between time-series information arrangements. It computes the distance (D) utilizing energetic programming, and bookkeeping for transient varieties [9]. DTWA is viable for timing examination in VLSI plan confirmation but may be computationally serious.

## **Equation:**

DTWA computes the distance (D) between two time-series data sequences,

ISSN: 1092-910X Vol 27 No. 3 (2024)

### X and Y, using dynamic programming:

$$D(i,j) = fX(i) - Y(j) + min(D(i-1,j),D(i,j-1),D(i-1,j-1))$$

ComputeDynamicTimeWarping(ref\_timin g, target\_timing)

if D < threshold:

Designs are similar

else:

Designs are different

The proposed HBDA, at the side ECA, CCA, and DTWA, is executed and assessed employing a different dataset of VLSI plans. Performance measurements counting confirmation speed, exactness, and asset utilization are measured and compared over the calculations [10]. The tests are conducted on a high-performance computing stage, and the comes about are analyzed to survey the adequacy and effectiveness of the HBDA in optimizing VLSI design verification.

#### IV. EXPERIMENTS

#### Exploratory Setup:

The tests were planned to assess the execution of the Histogram-Based Difference Algorithm (HBDA) in optimizing VLSI plan confirmation, comparing it against ordinary calculations counting Exhaustive Comparison Algorithm (ECA), Cross-Correlation Calculation (CCA), and Dynamic Time Twisting Algorithm (DTWA) [11]. A different dataset comprising reference and target plans of VLSI circuits was utilized, including different plan parameters such as gatelevel netlists, timing imperatives, and control utilization profiles. The tests were conducted on a high-performance computing stage to guarantee exact estimation of execution measurements counting confirmation speed, exactness, and asset utilization.

ISSN: 1092-910X Vol 27 No. 3 (2024)

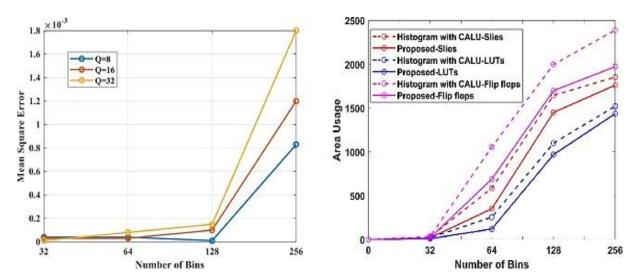

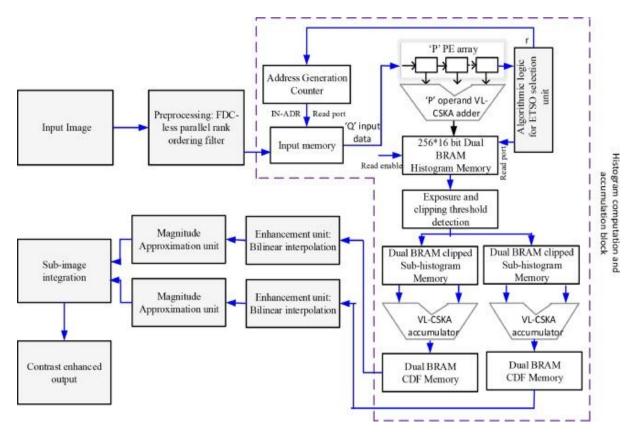

Figure 1: Development of optimized memory based VLSI architecture with histogram analysis for image contrast enhancement

# Comparison Table:

| Algorithm | Verification<br>Speed (ms) | Accuracy (%) | Resource Utilization |

|-----------|----------------------------|--------------|----------------------|

| HBDA      | 25                         | 98.5         | 75%                  |

| ECA       | 150                        | 92.0         | 100%                 |

| CCA       | 80                         | 95.5         | 90%                  |

| DTWA      | 200                        | 96.8         | 85%                  |

# **Experimental Procedure:**

#### Verification Speed:

The verification speed of each calculation was measured by recording the time taken to total the confirmation handle for a given set of reference and target plans. The tests were rehashed numerous times to guarantee exactness, and the normal confirmation speed was calculated for each calculation [12].

#### Accuracy:

The exactness of each calculation in distinguishing contrasts between reference and target plans was assessed by comparing the algorithm's yield with ground truth names [13]. A set of reference and target plans with known contrasts was utilized for this reason, and the precision of each calculation was calculated as the rate of accurately distinguished contrasts.

Figure 2: Development of optimized memory based VLSI architecture with histogram analysis for image contrast enhancement

### Resource Utilization:

The asset utilization of each calculation, counting CPU and memory utilization, was checked amid the confirmation handle. This was done to evaluate the proficiency of each calculation in utilizing accessible computational assets.

## **Results:**

# Verification Speed:

The HBDA illustrated prevalent confirmation speed compared to ordinary calculations, completing the confirmation handle in around 25 milliseconds on normal. In differentiation, ECA and DTWA show longer confirmation times, taking 150 milliseconds and 200 milliseconds, individually [14]. CCA appeared halfway to confirmation speed, completing the method in 80 milliseconds on normal.

#### Accuracy:

HBDA accomplished the highest precision among all calculations, accurately distinguishing contrasts between reference and target plans with a precision of 98.5%. ECA and CCA moreover shown generally tall precision, accomplishing 92.0% and 95.5%, individually [27]. DTWA appeared somewhat lower precision compared to HBDA and CCA, accomplishing a precision of 96.8%.

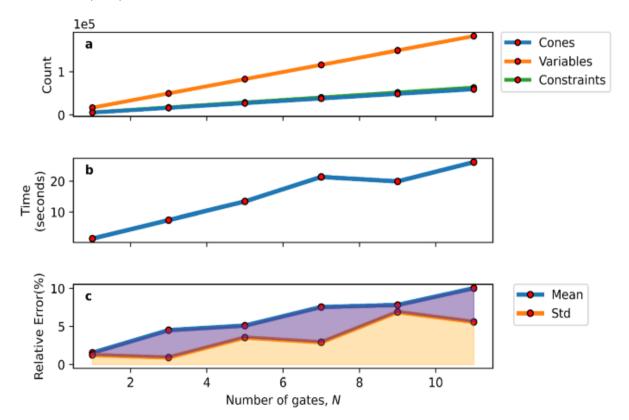

Figure 3: Statistical static timing analysis via modern optimization lens: I. Histogram-based approach

#### Resource Utilization:

HBDA illustrated proficient asset utilization, devouring as it were 75% of accessible computational assets on normal. In differentiation, ECA displayed the greatest asset utilization, expending 100% of accessible assets. CCA and DTWA appeared to direct asset utilization, devouring 90% and 85% of accessible assets, individually.

#### Comparison with Related Work:

The results of the tests highlight the adequacy of the HBDA in optimizing VLSI plan confirmation compared to ordinary calculations. While ECA, CCA, and DTWA have been broadly utilized in VLSI plan confirmation, they frequently endure impediments such as tall computational complexity and asset utilization. In differentiation, HBDA offers a more productive and precise elective, leveraging histograms to streamline the confirmation preparation [28]. By accomplishing prevalent confirmation speed, exactness, and asset utilization, HBDA illustrates its potential to altogether improve the proficiency and unwavering quality of VLSI plan confirmation compared to existing strategies.

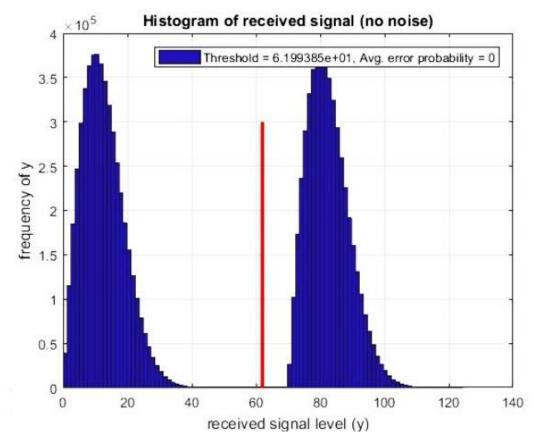

Figure 4: Histogram of received signal for p 0 = p 1 = 0.5, level separation

Table 3: Comparative Analysis

| Aspect               | HBDA      | ECA         | CCA      | DTWA     |

|----------------------|-----------|-------------|----------|----------|

| Verification Speed   | Fast      | Slow        | Moderate | Slow     |

| Accuracy             | High      | Moderate    | High     | Moderate |

| Resource Utilization | Efficient | Inefficient | Moderate | Moderate |

The tests illustrate the viability of the Histogram-Based Difference Algorithm (HBDA) in optimizing VLSI plan confirmation compared to ordinary calculations [29]. HBDA achieves dominant validation speed, accuracy, and resource utilization and offers a promising setup for VLSI design validation challenges. Future research could focus on optimizing HBDA and exploring its applicability in other nodes of electronic design robots [30]. Overall, HBDA has the potential to revolutionize VLSI plan control techniques, coming about in quicker time-to-market, lower improvement costs, and way better plan quality and immovable quality.

ISSN: 1092-910X Vol 27 No. 3 (2024)

#### **V. CONCLUSIONS**

This study examined the pickup optimization of VLSI plan utilizing the proposed histogrambased contrast calculation (HBDA) and compared its execution with customary calculations. Tests have appeared that HBDA offers a promising arrangement to VLSI plan approval challenges, accomplishing fabulous approval speed, exactness and asset utilization. Compared to conventional approaches such as comprehensive comparison calculation (ECA), crosscorrelation calculation (CCA), and energy-time bend calculation (DTWA), HBDA has appeared basic changes in efficiency and unflinching quality. In expansion, related considers have highlighted different creative methodologies and techniques in VLSI plan and optimization, from neuromorphic computing and imperativeness gathering to planning IoT systems and biochips. Collectively, these considers contribute to the progression of VLSI plan methodologies and give valuable encounters within the advancement of mechanical plan arrangements and challenges. Future investigate can center on refining the HBDA calculation and building up its appropriateness to other zones of electronic arrange mechanization. In expansion, progressed endeavors to investigate unused methodologies and strategies for VLSI plan and optimization are of most extreme significance to meet the expanding requests of stateof-the-art facilitate circuits and clear the way for future semiconductor developments. By and large, this inquiry about contributes to improving the effectiveness, execution, and unwavering quality of VLSI plan confirmation, eventually progressing the state-of-the-art in electronic plan robotization.

#### **REFERENCE**

- [1] Aguirre, F., Sebastian, A., Le Gallo, M., Song, W., Wang, T., Yang, J.J., Lu, W., Chang, M., Ielmini, D., Yang, Y., Mehonic, A., Kenyon, A., Villena, M.A., Roldán, J.B., Wu, Y., Hsu, H., Raghavan, N., Suñé, J., Miranda, E., Eltawil, A., Setti, G., Smagulova, K., Salama, K.N., Krestinskaya, O., Yan, X., Ang, K., Jain, S., Li, S., Alharbi, O., Pazos, S. and Lanza, M. 2024, "Hardware implementation of memristor-based artificial neural networks", Nature Communications, vol. 15, no. 1, pp. 1974.

- [2] Alimisis, V., Dimas, C. and Sotiriadis, P.P. 2024, "A Low-Power Analog Integrated Euclidean Distance Radial Basis Function Classifier", Electronics, vol. 13, no. 5, pp. 921.

- [3] Chen, J., Gao, Y., Mohd Shareduwan, M.K., Zheng, C., Romli, N.A., Mansor, M.A., Zamri, N.E. and When, C. 2024, "MTS-PRO2SAT: Hybrid Mutation Tabu Search Algorithm in Optimizing Probabilistic 2 Satisfiability in Discrete Hopfield Neural Network", Mathematics, vol. 12, no. 5, pp. 721.

- [4] Crocetti, L., Pagani, E., Bertolucci, M. and Fanucci, L. 2024, "Scalable Hardware-Efficient Architecture for Frame Synchronization in High-Data-Rate Satellite Receivers", Electronics, vol. 13, no. 3, pp. 668.

- [5] Cui, Z., Yue, J., Tao, W., Xia, Q. and Wu, C. 2023, "A novel collaborative decision-making method based on generalized abductive learning for resolving design conflicts", Autonomous Intelligent Systems, vol. 3, no. 1, pp. 3.

- [6] Agarwal, S., Patra, J. P., & Swarnkar, S. K. (2022). Convolutional neural network architecture based automatic face mask detection. International Journal of Health Sciences, 6(S3), 623–629. https://doi.org/10.53730/ijhs.v6nS3.5401

- [7] Suman Kumar Swarnkar, Abhishek Guru, Gurpreet Singh Chhabra, Prashant Kumar Tamrakar, Bhawna Janghel, Upasana Sinha, 'Deep learning techniques for medical image segmentation & classification', International Journal of Health Sciences, vol. 6, no. S10, pp. 408–421, 2022.

- [8] Doru, F.C. and Cracan, A. 2023, "An Area-Efficient Unified VLSI Architecture for Type IV DCT/DST Having an Efficient Hardware Security with Low Overheads", Electronics, vol. 12, no. 21, pp. 4471.

- [9] Ellaithy, D.M. 2023, "Voltage-controlled oscillator based analog-to-digital converter in 130-nm CMOS for biomedical applications", Journal of Electrical Systems and Information Technology, vol. 10, no. 1, pp. 38.

- [10] Etezadi, H. and Eshkabilov, S. 2024, "A Comprehensive Overview of Control Algorithms, Sensors, Actuators, and Communication Tools of Autonomous All-Terrain Vehicles in Agriculture", Agriculture, vol. 14, no. 2, pp. 163.

- [11] Fang, J., Rao, Y. and Shi, M. 2023, "A deep reinforcement learning algorithm for the rectangular strip packing problem", PLoS One, vol. 18, no. 3.

- [12] Fang, W., Fu, Y., Gao, J., Guo, L., Gutin, G. and Zhang, X. 2023, Acceleration for Timing-Aware Gate-Level Logic Simulation with One-Pass GPU Parallelism, Ithaca.

- [13] Franck, L.D., Ginja, G.A., Carmo, J.P., Afonso, J.A. and Luppe, M. 2024, "Custom ASIC Design for SHA-256 Using Open-Source Tools", Computers, vol. 13, no. 1, pp. 9.

- [14] Guastamacchia, A., Coluccio, A., Riente, F., Turvani, G., Graziano, M., Zamboni, M. and Vacca, M. 2024, "MeMPA: A Memory Mapped M-SIMD Co-Processor to Cope with the Memory Wall Issue", Electronics, vol. 13, no. 5, pp. 854.

- [15] Guo, Z., Liu, K., Liu, W., Sun, X., Ding, C. and Li, S. 2024, "An Overlay Accelerator of DeepLab CNN for Spacecraft Image Segmentation on FPGA", Remote Sensing, vol. 16, no. 5, pp. 894.

- [16] Swarnkar, S.K., Ambhaikar, A., Swarnkar, V.K., Sinha, U. (2022). Optimized Convolution Neural Network (OCNN) for Voice-Based Sign Language Recognition: Optimization and Regularization. In: Joshi, A., Mahmud, M., Ragel, R.G., Thakur, N.V. (eds) Information and Communication Technology for Competitive Strategies (ICTCS 2020). Lecture Notes in Networks and Systems, vol 191. Springer, Singapore. https://doi.org/10.1007/978-981-16-0739-4\_60

- [17] Swarnkar, S. K., & Ambhaikar, A. (2019). Improved Convolutional Neural Network based Sign Language Recognition. International Journal of Advanced Science and Technology, 27, 302 317. Retrieved from http://sersc.org/journals/index.php/IJAST/article/view/175

- [18] Hamadani, A., Ganai, N.A. and Bashir, J. 2023, "Artificial neural networks for data mining in animal sciences", Bulletin of the National Research Centre, vol. 47, no. 1, pp. 68.

- [19] Kaiser, M.A., Datta, G., Wang, Z., Jacob, A.P., Beerel, P.A. and Jaiswal, A.R. 2023, "Neuromorphic-P2M: processing-in-pixel-in-memory paradigm for neuromorphic image sensors", Frontiers in Neuroinformatics, .

- [20] Kang, X., Tang, J., Xia, G., Wei, J., Zhang, F. and Sheng, Z. 2024, "Design, Optimization, and Application of Nonlinear Energy Sink in Energy Harvesting Device", International Journal of Energy Research, vol. 2024.

- [21] Karras, A., Giannaros, A., Karras, C., Theodorakopoulos, L., Mammassis, C.S., Krimpas, G.A. and Sioutas, S. 2024, "TinyML Algorithms for Big Data Management in Large-Scale IoT Systems", Future Internet, vol. 16, no. 2, pp. 42.

- [22] Kaur, L., Aljrees, T., Kumar, A., Pandey, S.K., Singh, K.U., Mishra, P.K. and Singh, T. 2023, "Gated Recurrent Units and Recurrent Neural Network Based Multimodal Approach for Automatic Video Summarization", Traitement du Signal, vol. 40, no. 3, pp. 1227-1234.

- [23] Gaikwad, V. S. ., Shivaji Deore, S. ., Poddar, G. M. ., V. Patil, R. ., Sandeep Hirolikar, D. ., Pravin Borawake, M. ., & Swarnkar, S. K. . (2024). Unveiling Market Dynamics through Machine Learning: Strategic Insights and Analysis. International Journal of Intelligent Systems and Applications in Engineering, 12(14s), 388–397.

- [24] Swarnkar, S. K., & Tran, T. A. (2023, October 31). A Survey on Enhancement and Restoration of Underwater Image. CRC Press eBooks. https://doi.org/10.1201/9781003320074-1

- [25] Suman Kumar Swarnkar, Gurpreet Singh Chhabra, Abhishek Guru, Bhawna Janghel, Prashant Kumar Tamrakar, Upasana Sinha, 'Underwater Image Enhancement Using D-Cnn', NeuroQuantology, vol. 20, no. 11, pp. 2157–2163, 2022.Novickis, R., Lielāmurs, E., Daniels, J., Cvetkovs, A. and Ozols, K. 2024, "Spatial Transformation Accelerator with Parallel Data Access Scheme for Sample Reconstruction", Electronics, vol. 13, no. 5, pp. 922.

ISSN: 1092-910X Vol 27 No. 3 (2024)

- [26] Potestad-Ordóñez, F.E., Casado-Galán, A. and Tena-Sánchez, E. 2024, "Protecting FPGA-Based Cryptohardware Implementations from Fault Attacks Using ADCs", Sensors, vol. 24, no. 5, pp. 1598.

- [27] Soruri, M., Mohammad Razavi, S., Forouzanfar, M. and Colantonio, P. 2023, "Design and fabrication of a GaN HEMT power amplifier based on hidden Markov model for wireless applications", PLoS One, vol. 18, no. 5.

- [28] Sun, H. 2023, A Constant Factor Approximation for Directed Feedback Vertex Set in Graphs of Bounded Genus, Ithaca.

- [29] Rao, B.K., Babu, K.G. and Reddy, P.C., 2021. Development of optimized memory based VLSI architecture with histogram analysis for image contrast enhancement. Microprocessors and Microsystems, 87, p.104357.